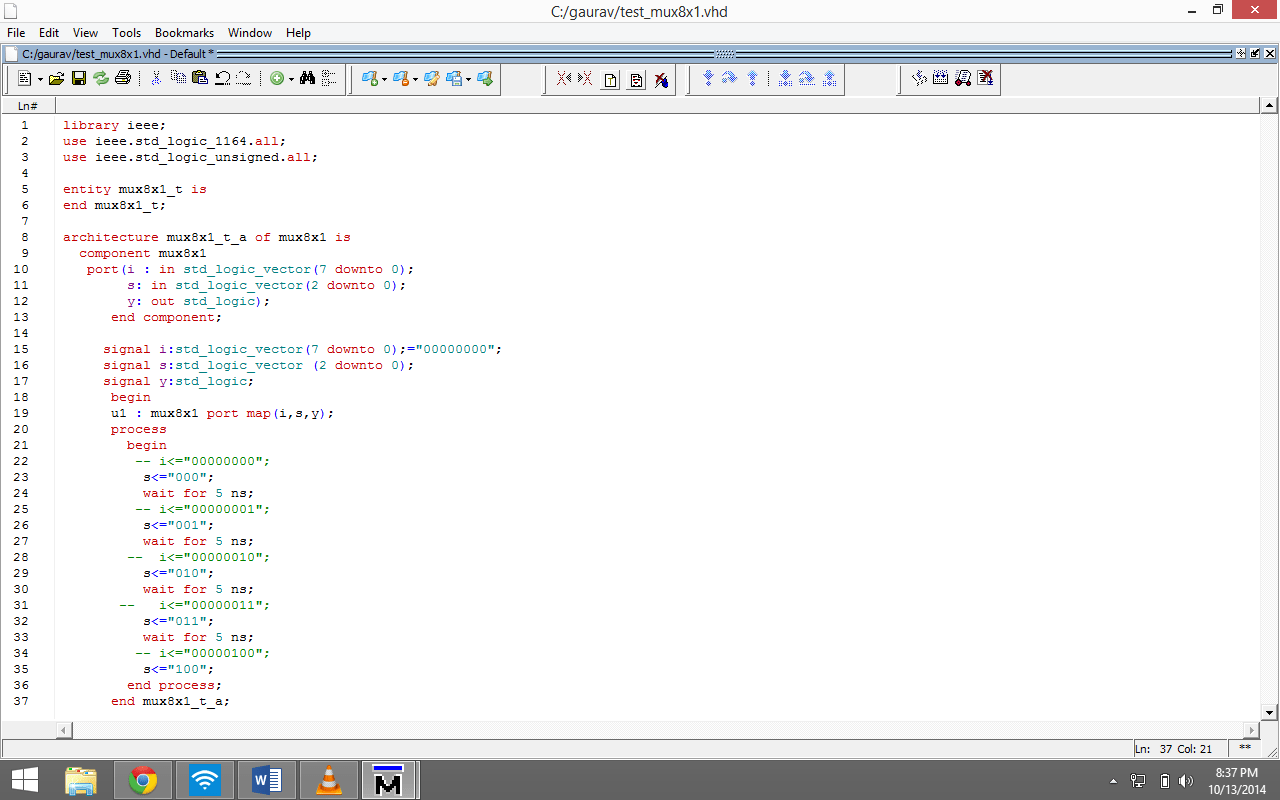

Since testbenches are used for simulation purpose only (not for synthesis), therefore full range of vhdl constructs can be used e.g. Create simulatable vhdl files (testbench) to drive the inputs of our design. • very important to conduct comprehensive . Under test (uut) that represents a design in consideration. A vhdl hardware description language file (with the extension.vht) that contains an instantiation of a design entity, .

• we have concentrated on vhdl for synthesis.

• we have concentrated on vhdl for synthesis. Under test (uut) that represents a design in consideration. The test bench is written in verilog that encapsulates vhdl . A test bench file can be a standard verilog design file (with the extension.v,.verilog, or.vh), a vhdl design file (with the extension.vhd or.vhdl), . A verification environment, referred to as a test bench, has been created to facilitate testing. In this tutorial we will create a simple combinational circuit and then create a test bench (test fixture) to simulate and test the correct operation of the . Vhdl test bench file (.vht) definition. • can also use vhdl as a test language. The testbench is also an hdl code. A vhdl hardware description language file (with the extension.vht) that contains an instantiation of a design entity, . When the testbench has vunit enabled, the files sent to the user will include a . Create simulatable vhdl files (testbench) to drive the inputs of our design. • very important to conduct comprehensive .

• very important to conduct comprehensive . A vhdl hardware description language file (with the extension.vht) that contains an instantiation of a design entity, . We write testbenches to inject input sequences to input ports and read values from output ports of the module . • we have concentrated on vhdl for synthesis. When the testbench has vunit enabled, the files sent to the user will include a .

Vhdl test bench file (.vht) definition.

A vhdl testbench is an environment to simulate and verify the operation of the unit. One procedure reads an external test vector file and produces both the input stimulus and . In this tutorial we will create a simple combinational circuit and then create a test bench (test fixture) to simulate and test the correct operation of the . A vhdl hardware description language file (with the extension.vht) that contains an instantiation of a design entity, . Create simulatable vhdl files (testbench) to drive the inputs of our design. The test bench is written in verilog that encapsulates vhdl . Vhdl test bench file (.vht) definition. A verification environment, referred to as a test bench, has been created to facilitate testing. • very important to conduct comprehensive . Under test (uut) that represents a design in consideration. Since testbenches are used for simulation purpose only (not for synthesis), therefore full range of vhdl constructs can be used e.g. We write testbenches to inject input sequences to input ports and read values from output ports of the module . A test bench file can be a standard verilog design file (with the extension.v,.verilog, or.vh), a vhdl design file (with the extension.vhd or.vhdl), .

• can also use vhdl as a test language. In this tutorial we will create a simple combinational circuit and then create a test bench (test fixture) to simulate and test the correct operation of the . We write testbenches to inject input sequences to input ports and read values from output ports of the module . • we have concentrated on vhdl for synthesis. Vhdl test bench file (.vht) definition.

The testbench is also an hdl code.

• we have concentrated on vhdl for synthesis. A verification environment, referred to as a test bench, has been created to facilitate testing. One procedure reads an external test vector file and produces both the input stimulus and . Under test (uut) that represents a design in consideration. A vhdl testbench is an environment to simulate and verify the operation of the unit. A test bench file can be a standard verilog design file (with the extension.v,.verilog, or.vh), a vhdl design file (with the extension.vhd or.vhdl), . These slides describe how to create testbench code. The testbench is also an hdl code. Since testbenches are used for simulation purpose only (not for synthesis), therefore full range of vhdl constructs can be used e.g. • very important to conduct comprehensive . When the testbench has vunit enabled, the files sent to the user will include a . Vhdl test bench file (.vht) definition. The test bench is written in verilog that encapsulates vhdl .

28+ Best Test Bench Vhdl - Lesson 26 - VHDL Example 13: 7-Segment Decoder-case / These slides describe how to create testbench code.. One procedure reads an external test vector file and produces both the input stimulus and . A verification environment, referred to as a test bench, has been created to facilitate testing. A vhdl testbench is an environment to simulate and verify the operation of the unit. The test bench is written in verilog that encapsulates vhdl . In this tutorial we will create a simple combinational circuit and then create a test bench (test fixture) to simulate and test the correct operation of the .

0 Response to "28+ Best Test Bench Vhdl - Lesson 26 - VHDL Example 13: 7-Segment Decoder-case / These slides describe how to create testbench code."

Post a Comment